热门搜索:

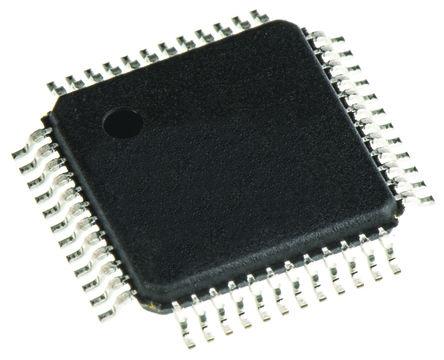

PY32F403C4T6

内置存储器

⚫ 较大384K字节内置闪存

⚫ 较大64K字节内置SRAM

Arm® Cortex®-M4处理器使用Harvard结构,指令和数据分开存取,提高执行速度,提高数据吞吐率。

表 5-1 存储器映射表定义了包括代码,SRAM,外设等区域的地址空间。

3.3 存储器保护单元(MPU)

存储器保护单元(MPU)用于管理CPU对存储器的访问,防止一个任务意外损坏另一个任务所使

用的存储器或资源。此存储区被组织为较多8个保护区,还可依次再被分为较多8个子区。保护区大小

可为 32 字节至可寻址存储器的整个4G字节。

若应用中有一些关键的或认的代码必须受到保护,以免被其它任务的错误行为影响,则MPU 尤其

有用。它通常由RTOS(实时操作系统)管理。若程序访问的存储器位置被MPU禁止,则RTOS可检

测到它并采取行动。在RTOS环境中,内核可基于执行的进程,动态更新MPU区的设置。MPU是可选

PY32F403XX Datasheet Rev0.6

Puya Semiconductor Page 9 of 68

的,若应用不需要则可绕过。

3.4 总线矩阵(Bus Matrix)

32位的multi-AHB总线矩阵将所有主设备(CPU、 DMA)和从设备(Flash、 RAM、 FMC、 AHB、

APB 外设)互连,确保了即使多个高速外设同时工作时,工作也能无缝、。

3.5 DMA控制器

该器件具有两个通用双端口 DMA(DMA1和DMA2),分别有7个和5个通道。它们能够管理存储器到

存储器、外设到存储器、存储器到外设的传输。它们具有用于APB/AHB外设的**FIFO,支持突发

传输,其设计可提供较大外设带宽(AHB/APB)。

这两个DMA控制器支持循环缓冲区管理,当控制器到达缓冲区末尾时,*专门代码。这两个DMA

控制器还有双缓冲特性,可自动使用和切换两个存储器缓冲,而不需要特殊代码。

每个数据流都与**的硬件DMA请求相连,同时支持软件触发。通过软件进行相关配置,并且数据源

和数据目标之间传输的数据量不受限制。

3.6 嵌入式Flash

器件内置了高达512K字节的Flash,可用于存储程序和数据。

3.7 片内RAM

器件内置了高达64K字节的RAM。。

3.8 循环冗余校验计算单元(CRC)

CRC(循环冗余校验)计算单元使用一个固定的多项式发生器从一个32位的数据字中产生CRC 码。

在众多的应用中,基于CRC的技术还常用来验证或存储的完整性。根据 EN/IEC60335-1 标

准的规定,这些技术提供了验Flash完整性的方法。CRC 计算单元有助于在运行期间计算软件的签

名,并将该签名与链接时生成并存储在*存储单元的参考签名加以比较。